隨著手機CPU廠商(高通、海思、三星、聯發科)的不斷發力,手機CPU都是四核、八核,聯發科甚至開始十核了,而且主頻也越來越高,因此絕大部分人認爲手機CPU可以和電腦CPU相媲美,但事實卻完全不是這樣。

說到CPU性能,就不得不先講清楚影響CPU性能的幾大關鍵因素:架構、工藝、主頻、核心等,絕不是簡簡單單的核數和主頻。

手機cpu和電腦cpu的性能比較

一、架構區別

簡單的來說,架構對于CPU來說就像一座建築的框架,作爲CPU最基本卻也是最重要的部分。手機CPU構架主要是基于ARM(高級精簡指令集機器Advanced RISC Machines)架構設計,而ARM用精簡指令系統(RISC),設計思想減少了大量CPU內部的指令集,造成ARM CPU性能至今一直都達不到英特爾X86 CPU的水平。

而電腦CPU采用的是X86、X64等架構,用複雜指令系統(CISC),最終結果是采用ARM架構的CPU,運算能力大大低于電腦CPU的運算能力,同等頻率CPU浮點運算能力相差在幾千到上萬倍。

有人一定會說,那爲什麽手機CPU不也采用X86、X64等架構,這是因爲定位問題決定的,手機的CPU必須滿足功耗低、廉價,而X86、X64等架構CPU確實無法滿足這一點。

四、GPU核心

一般來說,手機GPU是與CPU封裝在一起的在同一塊SoC上,相當intel的核芯顯卡。而電腦則不同,早期電腦的CPU通常都是主攻運算,視頻和圖形處理都交給顯卡,顯卡集成在北橋中。

後來有了獨立顯卡,而集顯慢慢的集成到了CPU中,而現在核心顯卡正在慢慢替代集顯了。值得一提的是,Intel最新的核芯顯卡功耗、性能都相當優秀,大有取代獨立顯卡的趨勢。

影響CPU性能的因素盤點

1、主頻

主頻也叫時鍾頻率,單位是兆赫(MHz)或千兆赫(GHz),用來表示CPU的運算、處理數據的速度。

CPU的主頻=外頻&TI mes;倍頻系數。很多人認爲主頻就決定著CPU的運行速度,這不僅是片面的,而且對于服務器來講,這個認識也出現了偏差。至今,沒有一條確定的公式能夠實現主頻和實際的運算速度兩者之間的數值關系,即使是兩大處理器廠家Intel(英特爾)和AMD,在這點上也存在著很大的爭議,從Intel的産品的發展趨勢,可以看出Intel很注重加強自身主頻的發展。

像其他的處理器廠家,有人曾經拿過一塊1GHz的全美達處理器來做比較,它的運行效率相當于2GHz的Intel處理器。主頻和實際的運算速度存在一定的關系,但並不是一個簡單的線性關系。所以,CPU的主頻與CPU實際的運算能力是沒有直接關系的,主頻表示在CPU內數字脈沖信號震蕩的速度。在Intel的處理器産品中,也可以看到這樣的例子:1 GHz Itanium芯片能夠表現得不多跟2.66 GHz至強(Xeon)/Opteron一樣快,或是1.5 GHz Itanium 2大約跟4 GHz Xeon/Opteron一樣快。CPU的運算速度還要看CPU的流水線、總線等等各方面的性能指標。

主頻和實際的運算速度是有關的,只能說主頻僅僅是CPU性能表現的一個方面,而不代表CPU的整體性能。

2、外頻

外頻是CPU的基准頻率,單位是MHz。CPU的外頻決定著整塊主板的運行速度。通俗地說,在台式機中,所說的超頻,都是超CPU的外頻(當然一般情況下,CPU的倍頻都是被鎖住的)相信這點是很好理解的。但對于服務器CPU來講,超頻是絕對不允許的。前面說到CPU決定著主板的運行速度,兩者是同步運行的,如果把服務器CPU超頻了,改變了外頻,會産生異步運行,(台式機很多主板都支持異步運行)這樣會造成整個服務器系統的不穩定。

目前的絕大部分電腦系統中外頻與主板前端總線不是同步速度的,而外頻與前端總線(FSB)頻率又很容易被混爲一談,下面的前端總線介紹談談兩者的區別。

3、前端總線(FSB)頻率

前端總線(FSB)頻率(即總線頻率)是直接影響CPU與內存直接數據交換速度。有一條公式可以計算,即數據帶寬=(總線頻率&TI mes;數據位寬)/8,數據傳輸最大帶寬取決于所有同時傳輸的數據的寬度和傳輸頻率。比方,現在的支持64位的至強Nocona,前端總線是800MHz,按照公式,它的數據傳輸最大帶寬是6.4GB/秒。

外頻與前端總線(FSB)頻率的區別:前端總線的速度指的是數據傳輸的速度,外頻是CPU與主板之間同步運行的速度。也就是說,100MHz外頻特指數字脈沖信號在每秒鍾震蕩一億次;而100MHz前端總線指的是每秒鍾CPU可接受的數據傳輸量是100MHz&TI mes;64bit÷8bit/Byte=800MB/s。

其實現在“HyperTransport”構架的出現,讓這種實際意義上的前端總線(FSB)頻率發生了變化。IA-32架構必須有三大重要的構件:內存控制器Hub (MCH) ,I/O控制器Hub和PCI Hub,像Intel很典型的芯片組 Intel 7501、Intel7505芯片組,爲雙至強處理器量身定做的,它們所包含的MCH爲CPU提供了頻率爲533MHz的前端總線,配合DDR內存,前端總線帶寬可達到4.3GB/秒。

但隨著處理器性能不斷提高同時給系統架構帶來了很多問題。而“HyperTransport”構架不但解決了問題,而且更有效地提高了總線帶寬,比方AMD Opteron處理器,靈活的HyperTransport I/O總線體系結構讓它整合了內存控制器,使處理器不通過系統總線傳給芯片組而直接和內存交換數據。這樣的話,前端總線(FSB)頻率在AMD Opteron處理器就不知道從何談起了。

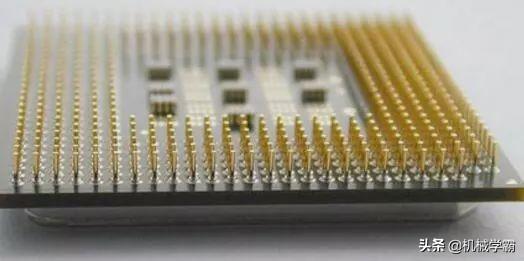

8、封裝形式

CPU封裝是采用特定的材料將CPU芯片或CPU模塊固化在其中以防損壞的保護措施,一般必須在封裝後CPU才能交付用戶使用。CPU的封裝方式取決于CPU安裝形式和器件集成設計,從大的分類來看通常采用Socket插座進行安裝的CPU使用PGA(柵格陣列)方式封裝,而采用Slot x槽安裝的CPU則全部采用SEC(單邊接插盒)的形式封裝。現在還有PLGA(Plastic Land Grid Array)、OLGA(Organic Land Grid Array)等封裝技術。由于市場競爭日益激烈,目前CPU封裝技術的發展方向以節約成本爲主。

9、多線程

同時多線程Simultaneous Multithreading,簡稱SMT。SMT可通過複制處理器上的結構狀態,讓同一個處理器上的多個線程同步執行並共享處理器的執行資源,可最大限度地實現寬發射、亂序的超標量處理,提高處理器運算部件的利用率,緩和由于數據相關或Cache未命中帶來的訪問內存延時。當沒有多個線程可用時,SMT處理器幾乎和傳統的寬發射超標量處理器一樣。

SMT最具吸引力的是只需小規模改變處理器核心的設計,幾乎不用增加額外的成本就可以顯著地提升效能。多線程技術則可以爲高速的運算核心准備更多的待處理數據,減少運算核心的閑置時間。這對于桌面低端系統來說無疑十分具有吸引力。Intel從3.06GHz Pentium 4開始,所有處理器都將支持SMT技術。

10、多核心

多核心,也指單芯片多處理器(Chip Multiprocessors,簡稱CMP)。CMP是由美國斯坦福大學提出的,其思想是將大規模並行處理器中的SMP(對稱多處理器)集成到同一芯片內,各個處理器並行執行不同的進程。與CMP比較, SMT處理器結構的靈活性比較突出。

但是,當半導體工藝進入0.18微米以後,線延時已經超過了門延遲,要求微處理器的設計通過劃分許多規模更小、局部性更好的基本單元結構來進行。相比之下,由于CMP結構已經被劃分成多個處理器核來設計,每個核都比較簡單,有利于優化設計,因此更有發展前途。目前,IBM 的Power 4芯片和Sun的 MAJC5200芯片都采用了CMP結構。多核處理器可以在處理器內部共享緩存,提高緩存利用率,同時簡化多處理器系統設計的複雜度。