即便都是7nm,但似乎都有些差異,甚至還有像三星這樣只“差”了1nm的8nm方案,這些還是值得我們去研究個中差別的。我們也期望通過粗淺地闡述不同7nm工藝在參數方面的差別,來大致看一看如今的工藝制程有著什麽樣的市場宣傳範式。

通過對不同7nm、8nm工藝的認識進一步加深,也有助于我們搞清楚這些數字實際意味著什麽,以及“摩爾定律”背後的這些晶體管現如今究竟在以怎樣的步伐邁進。

骁龍855有兩種7nm?

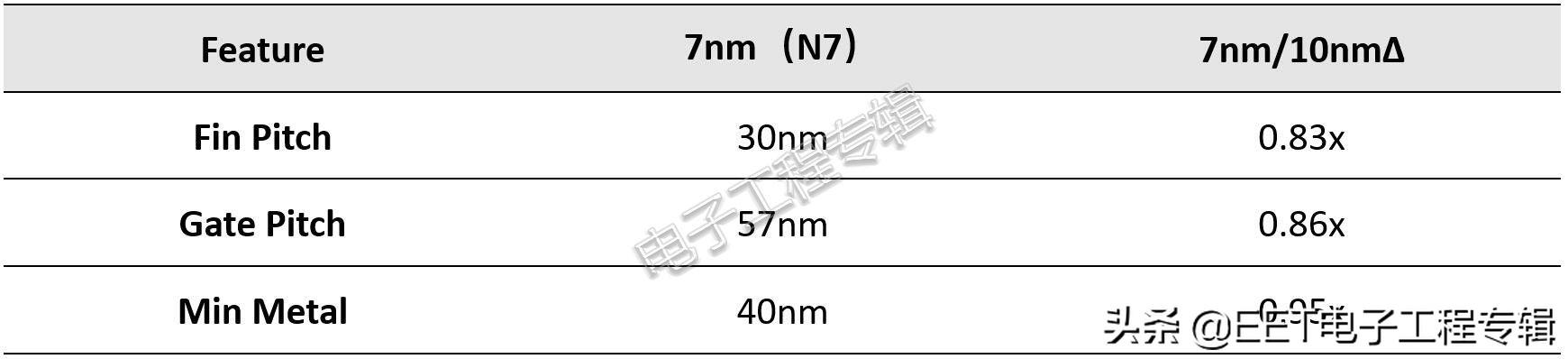

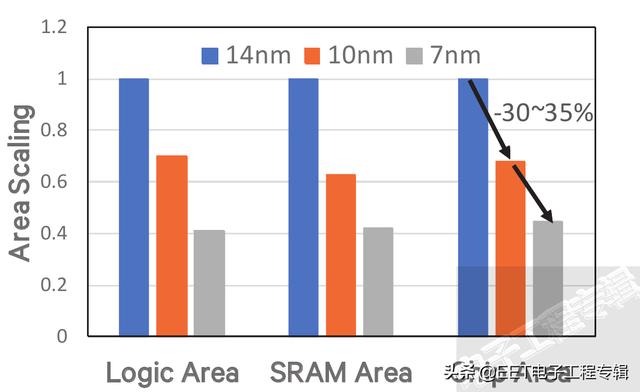

台積電(TSMC)是從2018年4月開始大規模量産7nm制程的。在台積電的規劃中,7nm是一個相對長期、完整的工藝節點——之前一代是16nm。而此間的10nm則屬于短期過渡方案。最早的這批TSMC 7nm方案,即上表中的N7(或N7FF)。它廣泛地應用在了高通骁龍855、華爲Kirin 990、AMD Zen 2這些SoC産品上。台積電宣稱相比16nm技術,7nm約有35-40%的速度提升,或降低了65%的功耗——這個值應用于真實SoC應該是很難真正實現的。

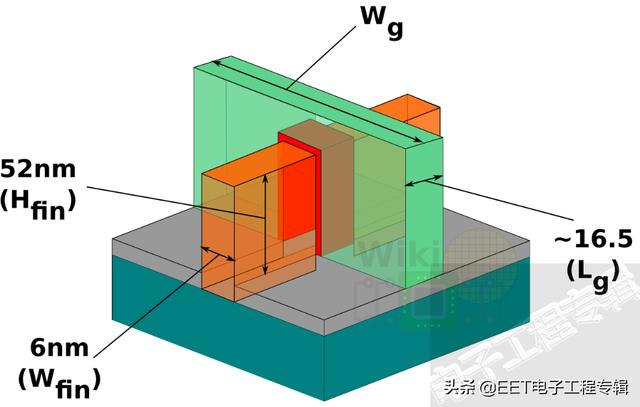

圖片來源:WikiChip

需要指出的是,上面的數據來自WikiChip[1],這個數據實際上與各廠商官方給出的數據略有出入,似乎與另外一些研究機構如TechInsights實際給出的數據也不一樣。比如就10nm這個節點,台積電最早給出的gate pitch爲64nm,interconnect pitch爲42nm;TechInsights在研究後認爲這個數據不准確,他們更傾向于這兩個值分別是66nm與44nm[2];WikiChip的數據則是66nm、42nm。本文給出的所有數據亦可能都不夠准確。

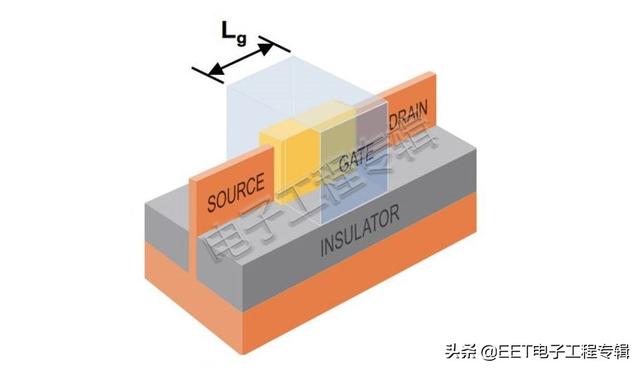

就單個晶體管本身來看,N7晶體管的溝槽接觸部分(trench contact)采用钴,代替了之前的鎢,這部分的電阻因此可以減少50%。fin 寬度(Wfin)、高度(Hfin)理論上也應當有變化(fin就是指FinFET鳍式場效應晶體管的那個“鳍”,即下圖中的橙色部分;淺綠色部分也就是gate)。縮減fin寬度實際上是讓溝道變窄了,而增加fin高度仍可維持一個相對有效的整體截面,減少寄生效應的同時可以加強有效電流(Ieff)、有效電容(Ceff)之類的特性。

論及standard cell(標准單元),這兩種方案的cell高度分別是240nm(6T/track,track是指走線軌道,信號線通常必須走在track上,standard cell高度可以用多少個track來表示,6T或6 track的意思就是在cell高度範圍內必須走6條線)和300nm(7.5T)。HP爲10 fin,HD爲8 fin。HP高性能cell可達成更高10-13%的有效驅動電流(Ieff),代價是略高一點的漏電流。

很顯然,這兩種方案的晶體管密度也是不同的。HD低功耗N7的晶體管密度爲91.2 MTr/mm²(MTr是指百萬個晶體管,這個單位的意思即百萬晶體管每平方毫米);HP高性能N7工藝晶體管密度65 MTr/mm²。這兩個數字具體是什麽量級呢?這將在後文的對比中提到。

圖片來源:華爲

海思Kirin 990 5G版也因此不僅是改換了modem模塊,而且在工藝及某些物理層上也是一次翻新。華爲在發布Kirin 990系列時就宣稱Kirin 990 5G是業內“首個使用EUV工藝打造的芯片”。所以Kirin 990 5G也的確一定程度推高了CPU和GPU的頻率,NPU的“大核心”還多加了一個。無奈並沒有分析機構給出Kirin 990 4G版本的die shot和芯片面積數據,所以也無法對比N7+在面積效率方面相比N7做出的提升。

值得一提的是,N7+的EUV光刻層是4層:就去年年中的消息來看,台積電還有更進一步的N6工藝節點,會采用更多的EUV層(似爲5層),雖然N6也並不是一個長期節點。而且N6在設計准則和IP方面,與N7兼容。也就是說芯片設計可以複用N7相同的設計生態,比如相同的工具,以直接降低開發成本。N7的設計可以在N6節點上再次流片,在EUV掩膜、保真度提升方面也有提升;PODE(poly over diffusion edge)與CNOD(continuous diffusion)standard cell能夠達成18%的密度提升。

N6和N7+似乎是兩條不同的路徑,因爲N7+並不能達成N6這樣的兼容性,且N7+實際有著密度方面略爲領先的優勢。這可能也是今年骁龍865並未選擇N7+的原因,N7P與未來的架構設計過渡可能將更加平緩。去年5月的財報電話會議上,台積電表示大部分N7客戶(而不是N7+客戶)最終都將轉往N6(6nm)工藝[4]。台積電預計是今年較早時間完成N6的風險生産,到今年年末以前達成良率和産量的提升——這個節點會與N5同期進行。

8nm:只差1nm的距離

和台積電針對7nm的態度不同,三星似乎很早就鐵了心要給7nm直接上EUV,而不像台積電那樣仍在早期的7nm方案中采用DUV和多重曝光。而在7nm EUV真正成熟以前,其過渡節點是一種名爲8nm LPP的工藝,聽起來也就少了1nm——雖然如今的這個數字不過就是個營銷名詞罷了。

采用8nm LPP相對知名的芯片也就是三星自家的Exynos 9820了,即應用于Galaxy S10手機的那款主SoC。在我們先前的對比文章中就不難發現,Exynos 9820相較同代、相近IP方案的産品,在性能和效率方面是多有不及的[5]。這個鍋當然不能完全由8nm LPP工藝來背,但8nm LPP也絕對是拖後腿的重要一環。

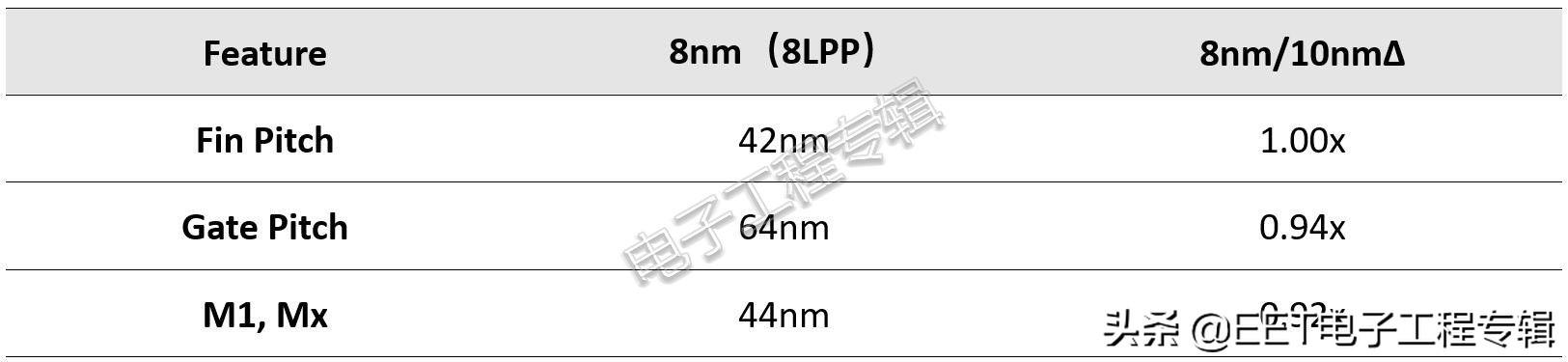

8nm LPP是三星最後一代完全的DUV工藝技術。三星認爲7nm的正確選擇一定是EUV,但在10nm和7nm之間又有個空缺位置,所以8nm就誕生了。從一些關鍵參數來看,8nm LPP更像是三星10nm的改良加強版。即便就其名稱來看,它與7nm十分接近。

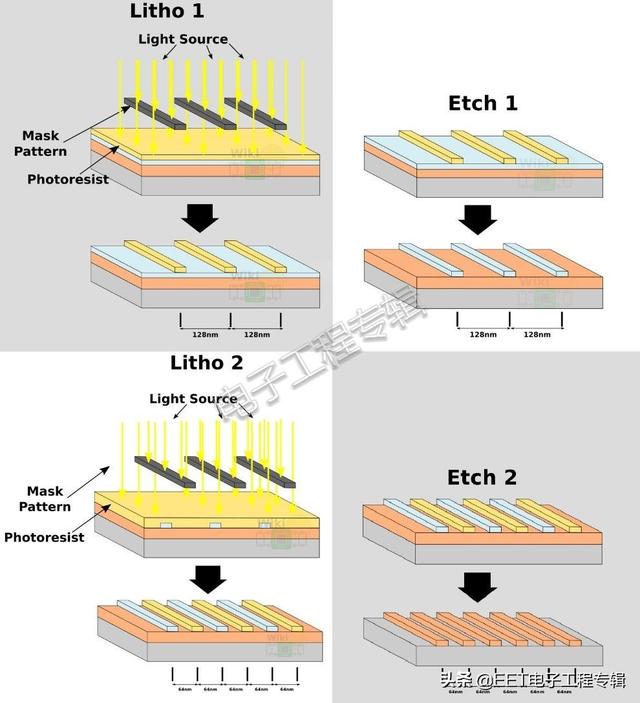

這裏我們簡單談一談LELE的原理,借此亦可理解DUV多重曝光的基本思路,即便不同方案的步驟會有差異[7]。首先如上圖所示,要有基底(substrate)、圖案層(device layer)、硬掩膜(hardmask)。在LELE方案中,如果我們要達成interconnect pitch(最小金屬間距)爲64nm,那麽就有了如下工序。

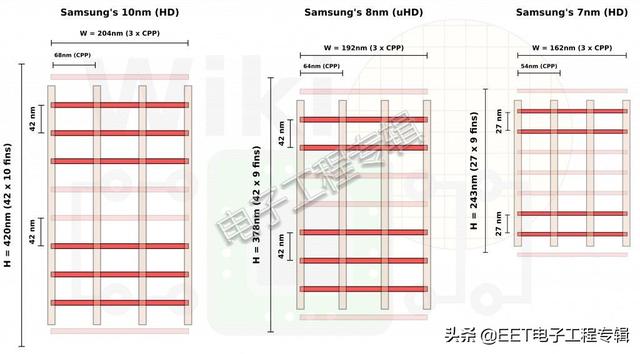

在8nm這代工藝節點上,三星也提供兩種standard cell方案,分別是HD高密度、uHD超高密度。其中HD cell和10nm LPP節點一致;uHD是全新的cell方案,去掉一個P fin,cell高度縮減至0.9倍。三星宣稱這種方案比之前的10LPP cell縮減了15%的邏輯面積。上面這張圖是NAND2門的10nm HD與8nm uHD工藝對比,還是能夠看到尺寸縮減的。

相對更具體地對比一下,三星10nm HD實現的晶體管密度大約51.8 MTri/mm²,8nm uHD可達成的晶體管密度爲61.2 MTr/mm²。這個值與台積電N7 HP高性能方案還比較接近,但和N7 HD高密度低功耗方案就有些距離了。

所以Imagination在發布會上說骁龍855的Adreno 640若爲100%面積,則Exynos 9820的Mali G76MP12需以184%的面積才能達到相同性能——GPU IP固然也是其中一部分原因,但前者采用台積電N7工藝,後者采用三星8nm LPP工藝,就不同的晶體管密度來看,工藝本身産生的影響也還是比較大的。

這組數據現在看來可能並不准確——尤其是在三星後續更新了路線圖和節點規劃之後。但如果就這組數字來看,是優于8nm LPP和台積電的N7、N7P的。。如果從standard cell來看,其高度縮減還是相當之大的,達到了243nm(6.75T),是8nm LPP的64%,10nm LPP的58%。一個NAND2 cell面積爲0.0394μm²,是8nm與10nm的54%和46%。

在談最先進半導體制造工藝的時候,2019年的SoC似乎絕大部分都可以統歸爲7nm。但是當我們去細看不同手機SoC甚至PC CPU的工藝制程時,大家的7nm似乎都有些差別。

來源:”Progress in EUV lithography toward manufacturing”, Proc. SPIE 10143, Extreme Ultraviolet (EUV

另外,EUV帶來的價值還包括(1)圖案保真度會明顯更高。傳統多重曝光技術的一大問題就是圖案保真度並不好,比如像上面這個圖案一樣,最終獲得的圖案與預期存在出入。三星表示,EUV 2D保真度相比ArF多重曝光要優秀70%;

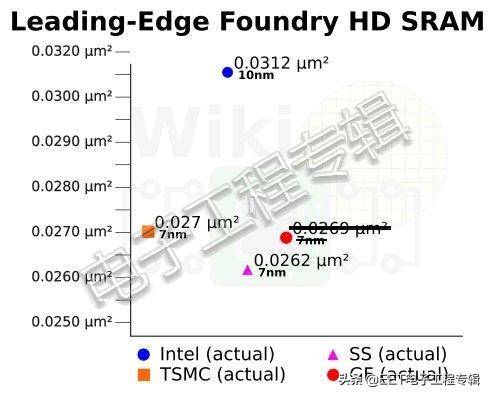

(2)設計彈性更大,比如雙向金屬配線(bi-directional metal routing),路徑、配線會變得更簡單;(3)更緊致的關鍵尺寸分布(CD distribution);(4)在SRAM cache存儲部分,單次曝光2D EUV,布局圖案變小至多50%,所以三星目前在SRAM部分相較其他競爭對手的同代工藝有著最高的密度,bit-cell尺寸爲0.0262μm²。

來源:WikiChips(注:我們對本圖進行了二次演繹)

上面這張圖並沒有算上台積電的N7+(和N6),若按台積電宣稱N7+的密度增加20%來算,台積電N7+的晶體管密度應該顯著高于三星的7LPP HD高密度cell方案,低于三星6LPP HD(密度提升18%)。另外,僅以密度判斷工藝成熟與否也是不科學的,這些數據僅作爲參考。

目前比較知名采用三星7nm LPP工藝的芯片應該就是Exynos 9825了——即應用于Galaxy Note 10手機的那顆SoC。實際上,Exynos 9820與9825是非常利于對比三星8nm與7nm工藝差別的兩款SoC,因爲9825實際各個層面的提升都不大,基本只有CPU的一組核心略加了頻率。不過市面上還沒有Exynos 9825的詳細數據,比如die size;從NoteBookCheck的測試數據來看,兩者未能表現出大差別。

Exynos 9825更像是三星的練手之作:三星似乎一直有這樣的傳統。多年前Exynos 5430,就各部分設計IP看來屬于Exynos 5422(Galaxy S5)的小升級;不過5430實際是三星在20nm工藝上的第一次練手,這顆芯片也從未大面積鋪貨,而作爲從中學習經驗的産品:Exynos 9825看起來也是如此。

無論今年蘋果A14將采用何種工藝(傳言稱由台積電N5節點全包攬),以及7nm這個節點的壽命還有多久,跨入EUV的厮殺顯然已經由Kirin 990 5G、Exynos 9825這些非大量出貨的SoC吹響了號角,7nm也是台積電和三星練手EUV的第一步。有關另一個尖端制造工藝的參與者:Intel的10nm與7nm,我們還將在未來的文章中做進一步的介紹。

更新:三星在後續發布的5nm、4nm路線圖中,更新了其7nm LPP工藝節點的信息(早前三星定義的7nm第二代,如今似已明確爲5nm LPE,原本的7nm LPE初代則已成爲明確的三星7nm節點——且當前已不分LPE與LPP)。因此本文最初呈現三星7nm LPP的數據有誤,現已在文中更正了三星7nm LPP節點的晶體管密度。請注意,初版數據與本文更新後的數據出入較大。